In my previous post about RF energy harvesting, I focused on a model for intentionally broadcasting RF energy to ensure the ambient energy in the environment was sufficient and consistent enough to power devices on demand that were located in difficult, unsafe, or expensive to reach locations. This approach is the basis for many RFID solutions. Using an intentional model of delivering energy by broadcasting can also simplify the energy harvesting system when the system only needs to operate in the presence of sufficient energy because the device may not need to implement a method of storing and managing the energy during periods of insufficient energy to harvest.

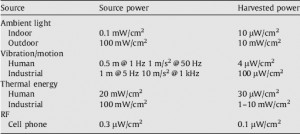

In addition to harvesting RF energy, designers have several options, such as thermal differentials, vibrations, and solar energy for extracting useful amounts of ambient energy. Which type(s) of energy a designer will choose to harness depends significantly on the specific location of the end device within the environment. The table identifies the magnitude of energy that a properly equipped device might expect to extract if placed in the appropriate location. The table also identifies the opportunities of extracting energy from a user by a wearable device. The amount of energy available from a human user is typically two to three orders of magnitude lower than that available in ideal industrial conditions.

The Micropower Energy Harvesting paper by R.J.M. Vullers, et al., provides a fair amount of detailed information about each type of energy harvesting approach that I summarize here. Solar or photovoltaic harvesters can collect energy from both outdoor and indoor light sources. Harvesting outdoor light offers the highest energy density when the device is being used in direct sun;however, harvesting indoor light can perform comparably with the other forms of energy harvesting listed in the table. Using photovoltaic harvesting indoors requires the use of fine-tuned cellsthat accommodate the different spectral composition of the light and the lower level of illumination than compared to outdoor lighting.

Harvesting energy from motion and vibration may use electrostatic, piezoelectric, or electromagnetic transducers. All vibration-harvesting systems rely on mechanical components that vibrate with a natural frequency close to that of the vibration source, such as a compressor, motor, pump, blowers, or even fans and ducts, to maximize the coupling between the vibration source and the harvesting system. The amount of energy that is extractable from vibrations usually scales with the cube of the vibration frequency and the square of the vibration amplitude.

Harvesting energy with electrostatic transducers relies on a voltage change across a polarized capacitor due to the movement of one moveable electrode. Harvesting energy with piezoelectric transducers relies on motion in the system causing the piezoelectric capacitor to deform which generates a voltage. Harvesting energy with electromagnetic transducers relies on a change in magnetic flux due to the relative motion of a magnetic mass with respect to a coil that generates an AC voltage acrossthe coil.

Harvesting energy from thermal gradients relies on the Seebeck effect where the junction made from two dissimilar conductors causescurrent to flow across the junction when the conductors are different temperatures. A thermopile, a device formed by a large number of thermocouples placed between a hot and cold plate, and which are connected thermally in parallel and electrically in series, is the core element of a thermal energy harvester. The power density of this energy harvesting technique increases as the temperature difference increases.

The majority of these harvesting systems has a relatively large size and is fabricated by standard or fine machining. The advances in research, development, and commercialization of MEMS promise to decrease the cost and increase the energy collection efficiency of energy harvesting devices.

If you would like to be an information source for this series or provide a guest post, please contact me at Embedded Insights.

[Editor's Note: This was originally posted on the Embedded Master]